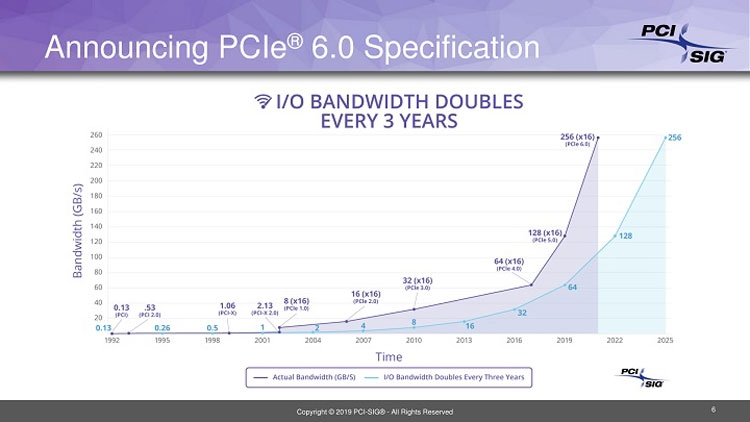

В мае этого года произошло два важных события. Во-первых, компания AMD объявила о выходе первых процессоров с поддержкой интерфейса PCI Express 4.0. Во-вторых, вышли финальные спецификации PCI Express версии 5.0. Эта накладка произошла по причине затянувшего выхода на рынок шины PCIe 4.0. Согласно ранее устоявшейся традиции, каждая новая версия PCI Express должна была выходить раз в три года. Шина PCIe 4.0 нарушила этот порядок и задержалась у разработчиков на семь долгих лет. Выход чистовых спецификаций PCIe 5.0 и PCIe 6.0 должны исправить это положение. Спецификации PCIe 6.0 разработчики обещают принять в окончательном виде в 2021 году и через год–два после этого ожидают на рынке появление решений с этим обновлённым интерфейсом.

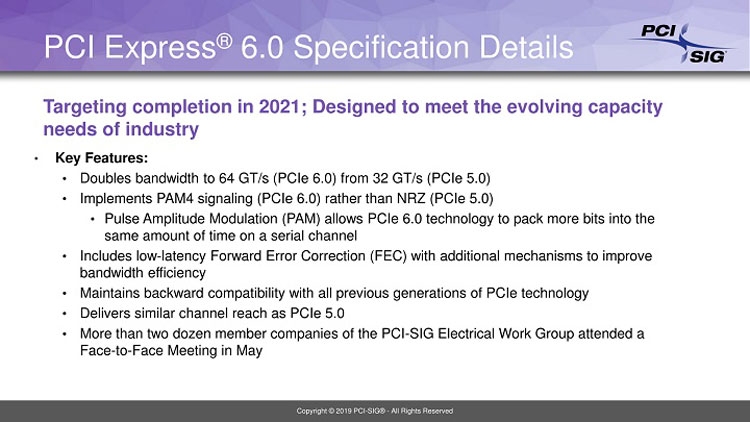

Согласно другой традиции, переход к новой версии снова в два раза увеличит скорость передачи данных: теперь с 32 гигатранзакций в секунду до 64 гигатранзакций в секунду (в пересчёте на 8 линий). Для достижения улучшенных показателей разработчики изменят сигнальную структуру интерфейса. Так, вместо передачи последовательности импульсов без возврата к нулю (NRZ, no-return-to-zero) будет реализована схема передачи с амплитудно-импульсной модуляцией (PAM4). На практике вместо последовательности 0 и 1 будет использоваться градация сигнала с четырьмя уровнями. Это очевидным образом увеличит плотность передачи данных и ёмкость канала, но это также чревато увеличением задержек.

В организации PCI Special Interest Group (SIG) пока не определились с уровнем задержек в стандарте PCIe 6.0. По мнению специалистов, латентность составит до десятков наносекунд, как у памяти типа DRAM. Основной вклад в рост задержек принесёт новый способ коррекции ошибок. Технология PAM4 требует перейти на прямое исправление ошибок за счёт избыточности или FEC (requires forward error correction). Обе эти технологии отсутствуют в спецификациях PCIe 5.0. Требование к обратной совместимости устройств с поддержкой PCI Express заставит разрабатывать механизмы переключения между NRZ и PAM4, что явно не сделает решения с поддержкой PCIe 6.0 дешевле и проще.

Другим важным моментом перехода на PCIe 6.0 станет удорожание комплектующих и материалов для плат. С ростом скорости передачи данных эффективная дальность линий снижается. Чтобы компенсировать это, нужны материалы, снижающие взаимные помехи сигналов от разных линий и различные волновые эффекты в линиях. Такое сырьё есть и оно уже используется в решениях для передачи данных по медным кабелям на скоростях свыше 200 Гбит/с. Что касается схемотехники, то с ростом скорости нужно вводить такие элементы как ретаймеры. Это чипы, которые восстанавливают целостность синхроимпульсов в условиях помех или слабого сигнала. Например, дальность передачи сигнала по спецификациям PCIe 4.0 составляет около 30 см без использования разъёмов. Спецификации PCIe 6.0 без специальных решений не смогут передать информацию даже на эту дистанцию.